VLSI Circuit Optimizations for Energy Efficiency

High energy efficiency is one of the primary targets in memory-centric computing designs. We develop advanced circuit and architecture techniques to further enhance the energy efficiency of memory-centric computing.

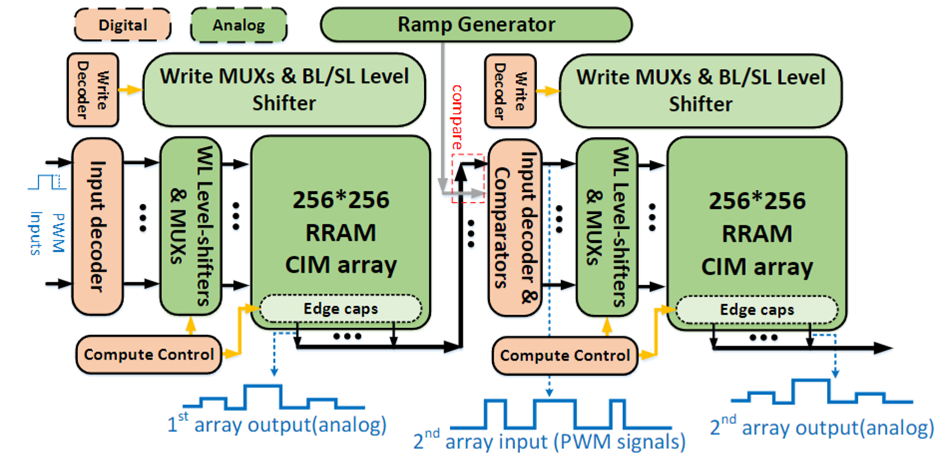

Previously we have proposed an RRAM-based compute-in-memory (CIM) macro with fully analog intra-/inter-array processing. The design avoids using explicit ADCs between subarrays to alleviate the energy efficiency bottleneck imposed by data domain conversions. A lightweight input-encoding scheme based on pulse-width modulation further improves the compute throughput.

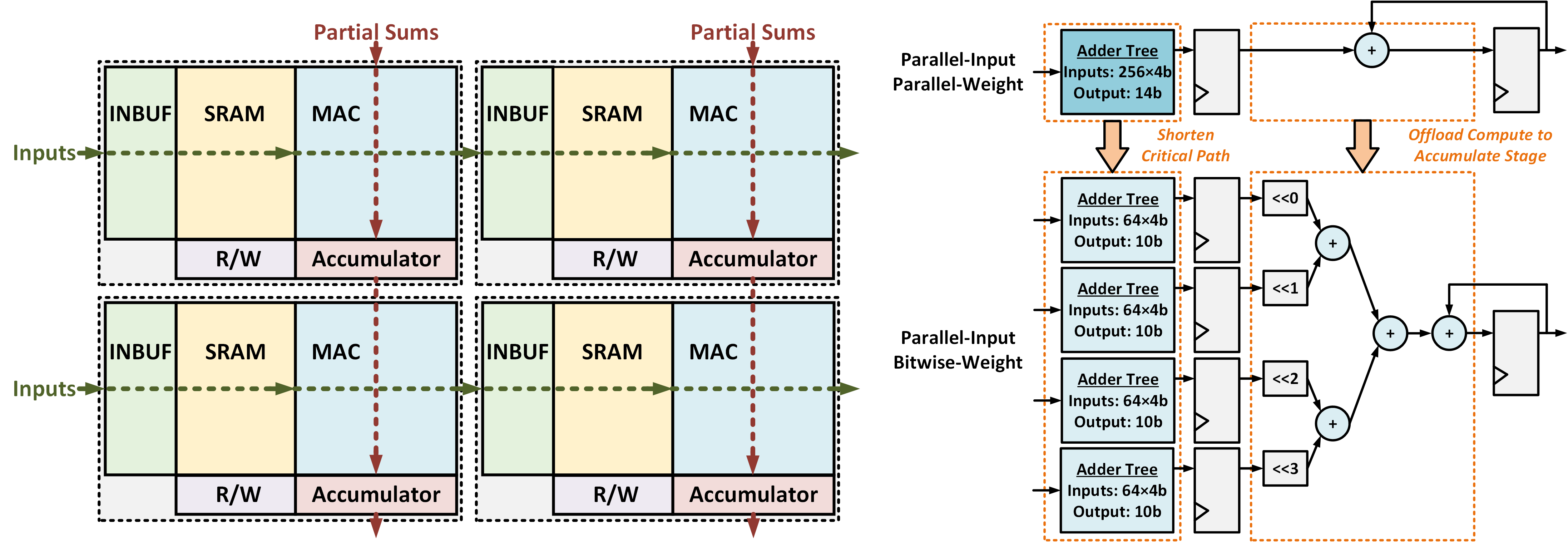

Besides analog and mixed-signal CIM, fully digital in-memory computing can be achieved by placing wide adder trees directly inside the memory arrays. One of the major drawbacks of digital CIM is its unfavorable scalability to larger array dimensions. By arranging digital CIM subarrays into a systolic configuration, while introducing a novel adder tree topology, we alleviate the scalability issue and demonstrate larger array sizes to hold more data.